- 您现在的位置:买卖IC网 > Sheet目录3891 > PIC18C801T-I/L (Microchip Technology)IC MCU ROMLESS A/D PWM 84PLCC

2001 Microchip Technology Inc.

Advance Information

DS39541A-page 101

PIC18C601/801

8.1.6

INT INTERRUPTS

External interrupts on the RB0/INT0, RB1/INT1 and

RB2/INT2 pins are edge triggered: either rising, if the

corresponding INTEDGx bit is set in the INTCON2 reg-

ister, or falling, if the INTEDGx bit is clear. When a valid

edge appears on the RBx/INTx pin, the corresponding

flag bit INTxIF is set. This interrupt can be disabled by

clearing the corresponding enable bit INTxIE. Flag bit

INTxIF must be cleared in software in the Interrupt Ser-

vice Routine before re-enabling the interrupt. All exter-

nal interrupts (INT0, INT1 and INT2) can wake-up the

processor from SLEEP, if bit INTxIE was set prior to

going into SLEEP. If the global interrupt enable bit GIE

is set, the processor will branch to the interrupt vector

following wake-up.

Interrupt priority for INT1 and INT2 is determined by the

value contained in the interrupt priority bits INT1IP

(INTCON3 register) and INT2IP (INTCON3 register).

There is no priority bit associated with INT0; it is always

a high priority interrupt source.

8.1.7

TMR0 INTERRUPT

In 8-bit mode (which is the default), an overflow

(0FFh

→ 00h) in the TMR0 register will set flag bit

TMR0IF. In 16-bit mode, an overflow (0FFFFh

→ 0000h)

in the TMR0H:TMR0L registers will set flag bit TMR0IF.

The interrupt can be enabled/disabled by setting/clear-

ing enable bit TMR0IE (INTCON register). Interrupt prior-

ity for Timer0 is determined by the value contained in the

interrupt priority bit TMR0IP (INTCON2 register). See

Section 10.0 for further details on the Timer0 module.

8.1.8

PORTB INTERRUPT-ON-CHANGE

An input change on PORTB<7:4> sets flag bit RBIF

(INTCON register). The interrupt can be enabled/

disabled by setting/clearing enable bit RBIE (INTCON

register). Interrupt priority for PORTB interrupt-on-

change is determined by the value contained in the

interrupt priority bit RBIP (INTCON2 register).

8.2

Context Saving During Interrupts

During an interrupt, the return PC value is saved on the

stack. Additionally, the WREG, STATUS and BSR regis-

ters are saved on the fast return stack. If a fast return

from interrupt is not used (See Section 4.3), the user

may need to save the WREG, STATUS and BSR regis-

ters in software. Depending on the user’s application,

other registers may also need to be saved. Example 8-1

saves and restores the WREG, STATUS and BSR

registers during an Interrupt Service Routine.

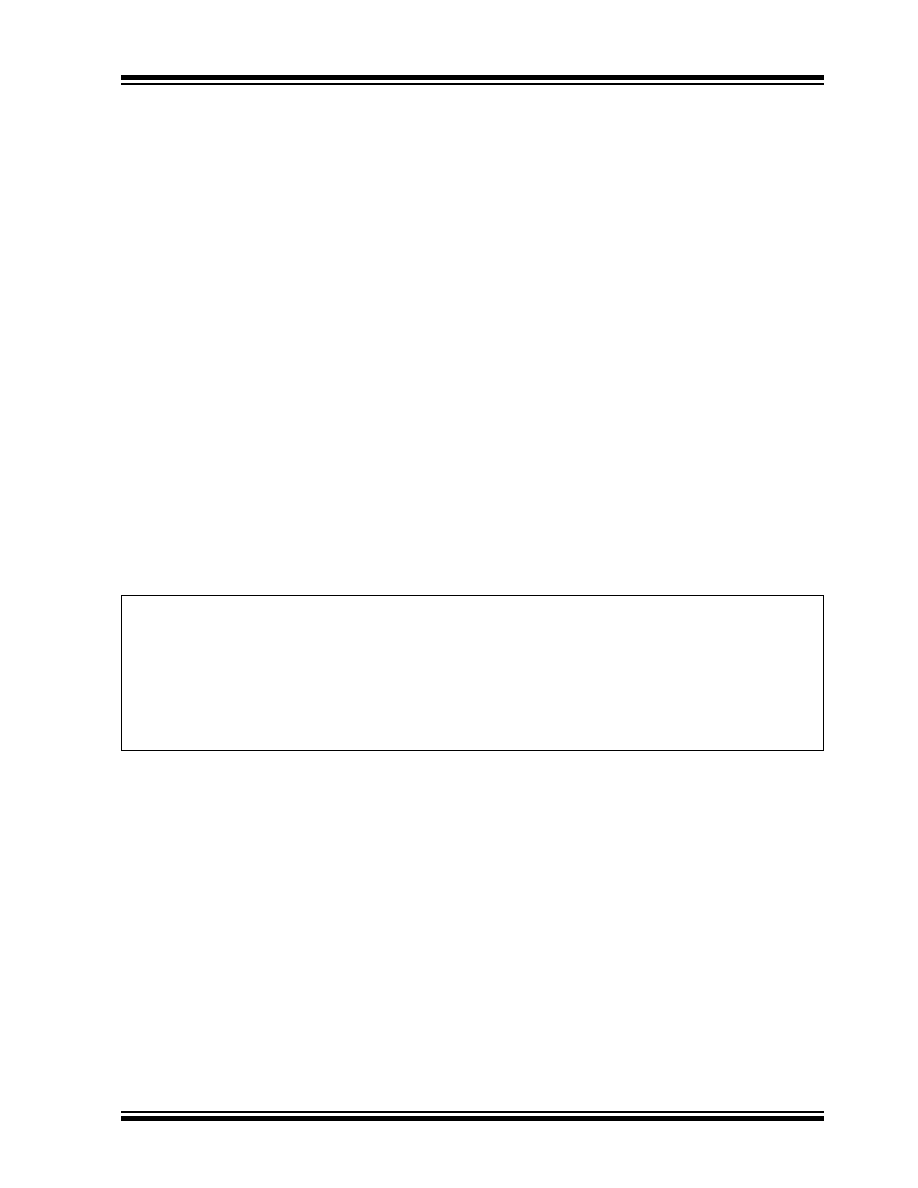

EXAMPLE 8-1:

SAVING STATUS, WREG AND BSR REGISTERS IN RAM

MOVWF

W_TEMP

; W_TEMP is in Low Access bank

MOVFF

STATUS, STATUS_TEMP

; STATUS_TEMP located anywhere

MOVFF

BSR, BSR_TEMP

; BSR located anywhere

;

; USER ISR CODE

;

MOVFF

BSR_TEMP, BSR

; Restore BSR

MOVF

W_TEMP, W

; Restore WREG

MOVFF

STATUS_TEMP, STATUS

; Restore STATUS

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18C658T-I/L

IC MCU OTP 16KX16 CAN 68PLCC

PIC18C658T-E/L

IC MCU OTP 16KX16 CAN 68PLCC

PIC16C925T-I/L

IC MCU OTP 4KX14 LCD DVR 68PLCC

PIC12F675-E/P

IC MCU CMOS 1K FLASH W/AD 8-DIP

PIC18C858T-E/L

IC MCU OTP 16KX16 CAN 84PLCC

PIC16F636-I/SL

IC PIC MCU FLASH 2KX14 14-SOIC

PIC18LC658T-I/L

IC MCU OTP 16KX16 CAN 68PLCC

PIC18LC801T-I/L

IC MCU ROMLESS A/D PWM 84PLCC

相关代理商/技术参数

PIC18C801T-I/PT

功能描述:8位微控制器 -MCU 2MB 1536 RAM 37I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858-E/L

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858-E/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858EPT

制造商:MICRO CHIP 功能描述:New

PIC18C858-I/L

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858-I/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858T-E/L

功能描述:8位微控制器 -MCU 40MHz 16K OTP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858T-E/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT